- **Das zugrundeliegende Schaltnetz: Selbsttestaufgabe 2.5**

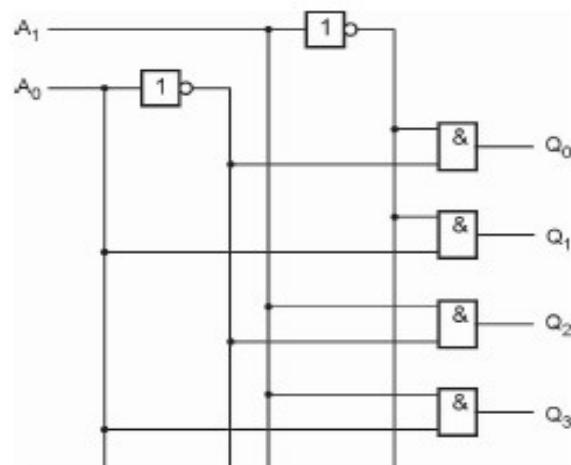

Entwerfen Sie die Funktionstabelle und ein Schaltnetz für einen 2-Bit Adressdecodierer.

Die Musterlösung lautet:

*Die Funktionstabelle ergibt sich wie folgt. Das Schaltnetz ist in Normalform in folgender Abbildung zu sehen:*

| $A_1$ | $A_0$ | $Q_3$ | $Q_2$ | $Q_1$ | $Q_0$ |

|-------|-------|-------|-------|-------|-------|

| 0     | 0     | 0     | 0     | 0     | 1     |

| 0     | 1     | 0     | 0     | 1     | 0     |

| 1     | 0     | 0     | 1     | 0     | 0     |

| 1     | 1     | 1     | 0     | 0     | 0     |

Quelle: Computersysteme I (2017), Kapitel 2.5.2 Schalnetzentwurf für einen Adressdecodierer

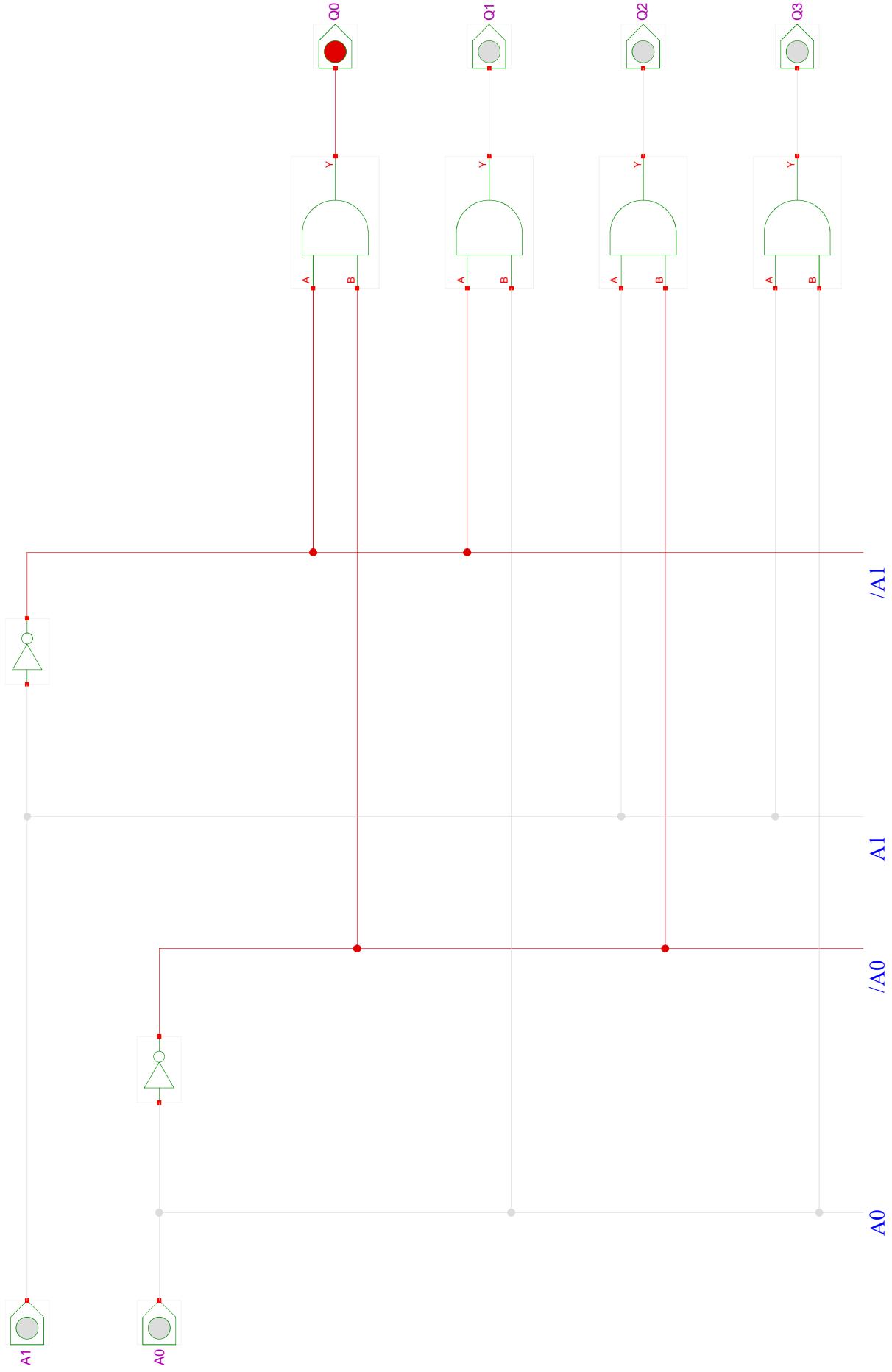

- **Die Hades Simulation:**

Der als letzte Seite angehängte Screenshot zeigt die exakte Umsetzung des obigen Schaltnetzes als Hades Simulation. Links sind die beiden Eingangssignale  $A_1, A_0$  platziert, rechts die vier Ausgangssignale für  $Q_0, \dots, Q_3$ .

Initial sind die Eingangssignale mit 0 (grau) vorbelegt, wodurch die erste Zeile der Funktionstabelle abgebildet wird. Entsprechend der Eingabe  $A_1 A_0 = 00$  ist die Ausgabe  $Q_3 Q_2 Q_1 Q_0 = 0001$ . Durch Klick auf die Schalter für die Eingangssignale können  $A_1$  und  $A_2$  mit 0 (grau) bzw. 1 (rot) belegt werden, sodass das Schaltverhalten beobachtet werden kann.

- **Die Simulation besteht aus folgenden Komponenten:**

- 2 Ipin (switch)

- 4 Opin (LED)

- 4 AND2

- 2 INV (small)