- **Das zugrundeliegende Schaltnetz: Selbsttestaufgabe 2.6**

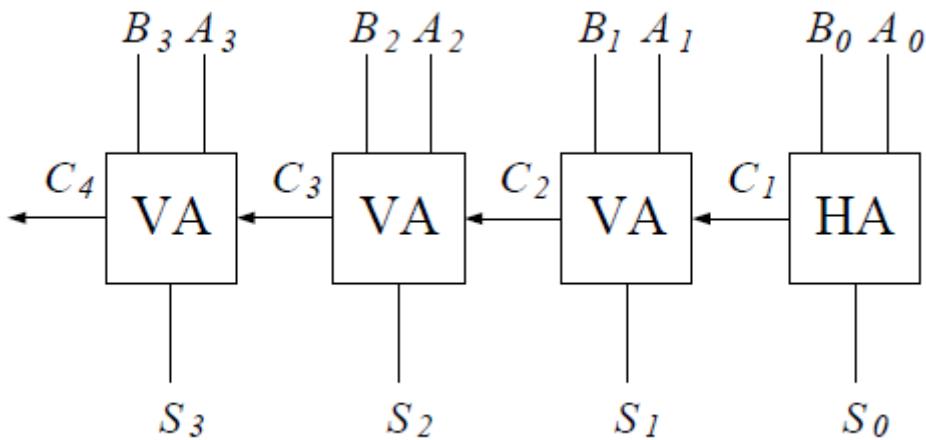

Konstruieren Sie aus Voll- und/oder Halbaddierern einen 4-Bit Ripple-Carry Addierer, der zusätzlich einen Eingangsübertrag  $C_0$  verarbeiten kann. Wie müssen Sie hierzu folgende Abbildung verändern?

Die Musterlösung lautet:

*Der Halbaddierer der niederwertigsten Stelle wird durch einen Volladdierer ersetzt, und der zusätzliche Eingang wird mit  $C_0$  verbunden.*

Quelle: Computersysteme I (2017), Kapitel 2.6.3 Paralleladdierer

- **Die Hades Simulation:**

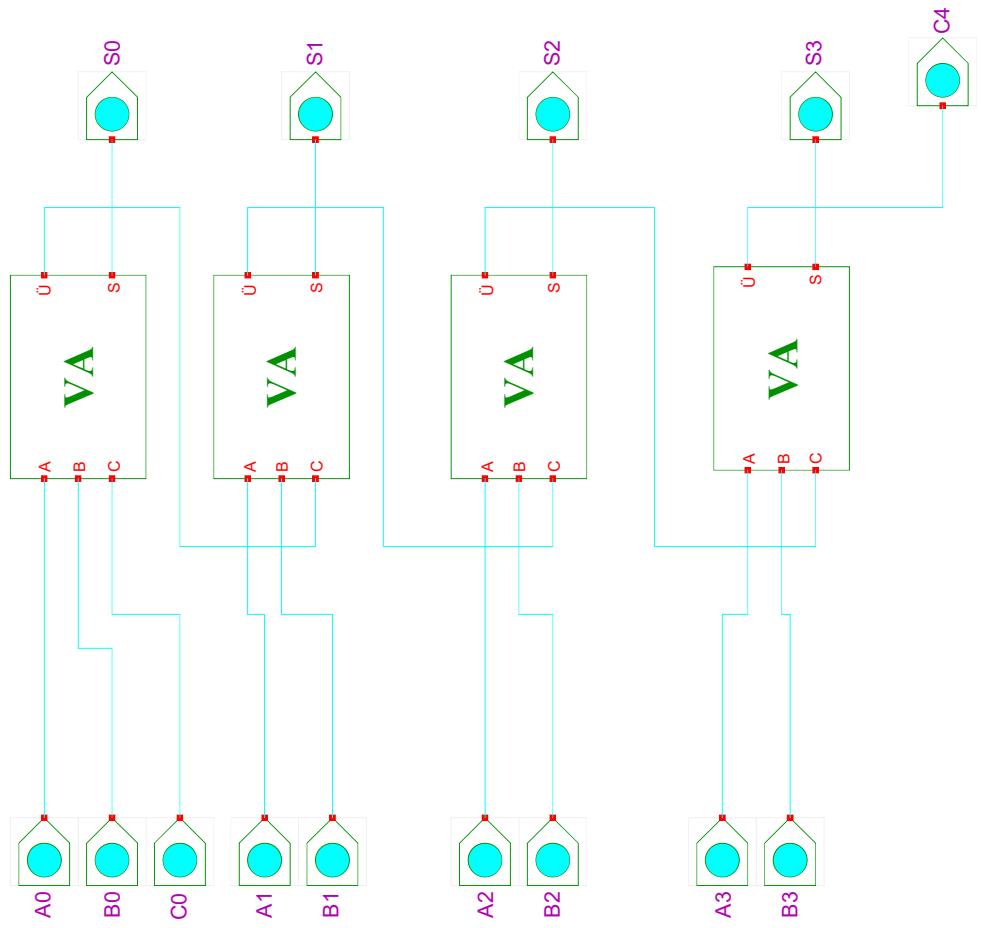

Der als letzte Seite angehängte Screenshot zeigt die Hades Umsetzung des 4-Bit Ripple-Carry Adders mit Eingangsübertrag. Links sind die Eingangssignale platziert, die die zu addierenden Bits und den Eingangsübertrag  $C_0$  realisieren, rechts stehen die 5 Ausgangssignale für die Summenbits  $S_0, \dots, S_3$  und den Ausgangsübertrag  $C_4$ . Der Eingangsübertrag wird mit  $A_0$  und  $B_0$  in den ersten Volladdierer geleitet, der resultierende Ausgangsübertrag ist dann der Eingangsübertrag für den nächsten VA, der  $A_1$  und  $B_1$  addiert, usw.

Initial ist der Adder im undefinierten Startzustand, zu erkennen an der Farbe cyan der Schalter und Verbindungen. Durch Klick auf die Schalter für die Eingangssignale kann man die Variablen mit 0 (grau) und 1 (rot) belegen und die Ausgabe an den Ausgangssignalen betrachten.

- **Die Simulation besteht aus folgenden Komponenten:**

- 9 Ipin (switch)      ◦ 4 VA      ◦ 5 Opin (LED)

- **Besonderheit:**

In dieser Simulation wurden *Subdesigns* verwendet. Die Symbole VA verstecken die Implementierung der zugrundeliegenden Volladdierer (siehe Simulation 06 dieser Reihe) und verfügen über die volle Funktionalität des enthaltenen Subdesigns. Wie bei allen verwendeten Subdesigns gilt auch hier: Klickt man mit der rechten Maustaste auf das Symbol und wählt im erscheinenden Popup-Menu den Eintrag *edit*, so öffnet sich das enthaltene Subdesign im Editor.