- **Das zugrundeliegende Schaltnetz: Selbsttestaufgabe 3.3**

Entwerfen Sie ein 3-Bit-Schieberegister, das folgende vier Funktionen ausführt:

| $S_1$ | $S_0$ | Funktion       |

|-------|-------|----------------|

| 0     | 0     | Rechtsschieben |

| 0     | 1     | Löschen        |

| 1     | 0     | Parallel Laden |

| 1     | 1     | Linksschieben  |

Hinweis: Verwenden Sie zum Entwurf 4:1-Multiplexer und D-Flipflops

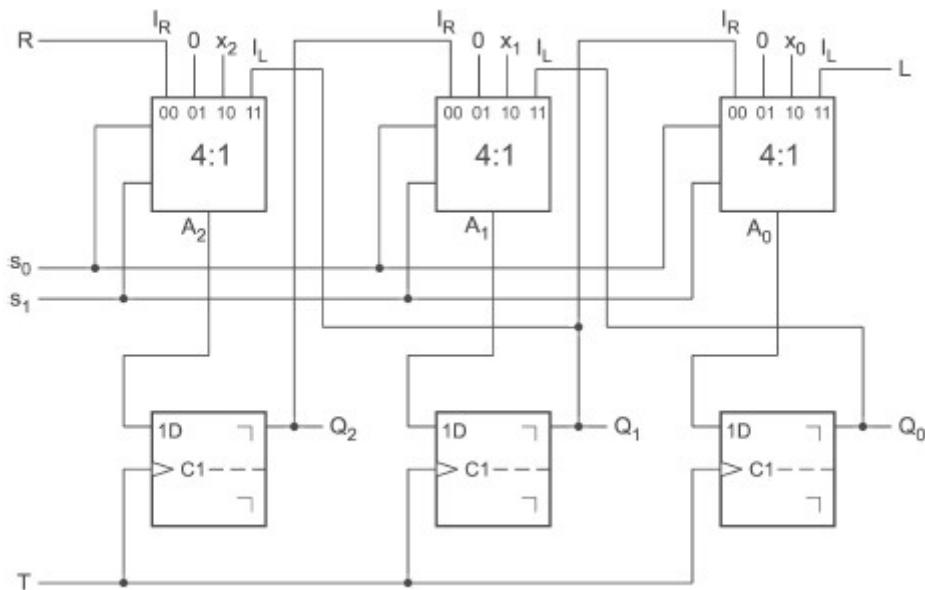

Musterlösung:

Die Lösung ist in folgender Abbildung dargestellt. Die Multiplexereingänge werden von links nach rechts über  $S_1 S_0 = 00, 01, 10$  und  $11$  ausgewählt:

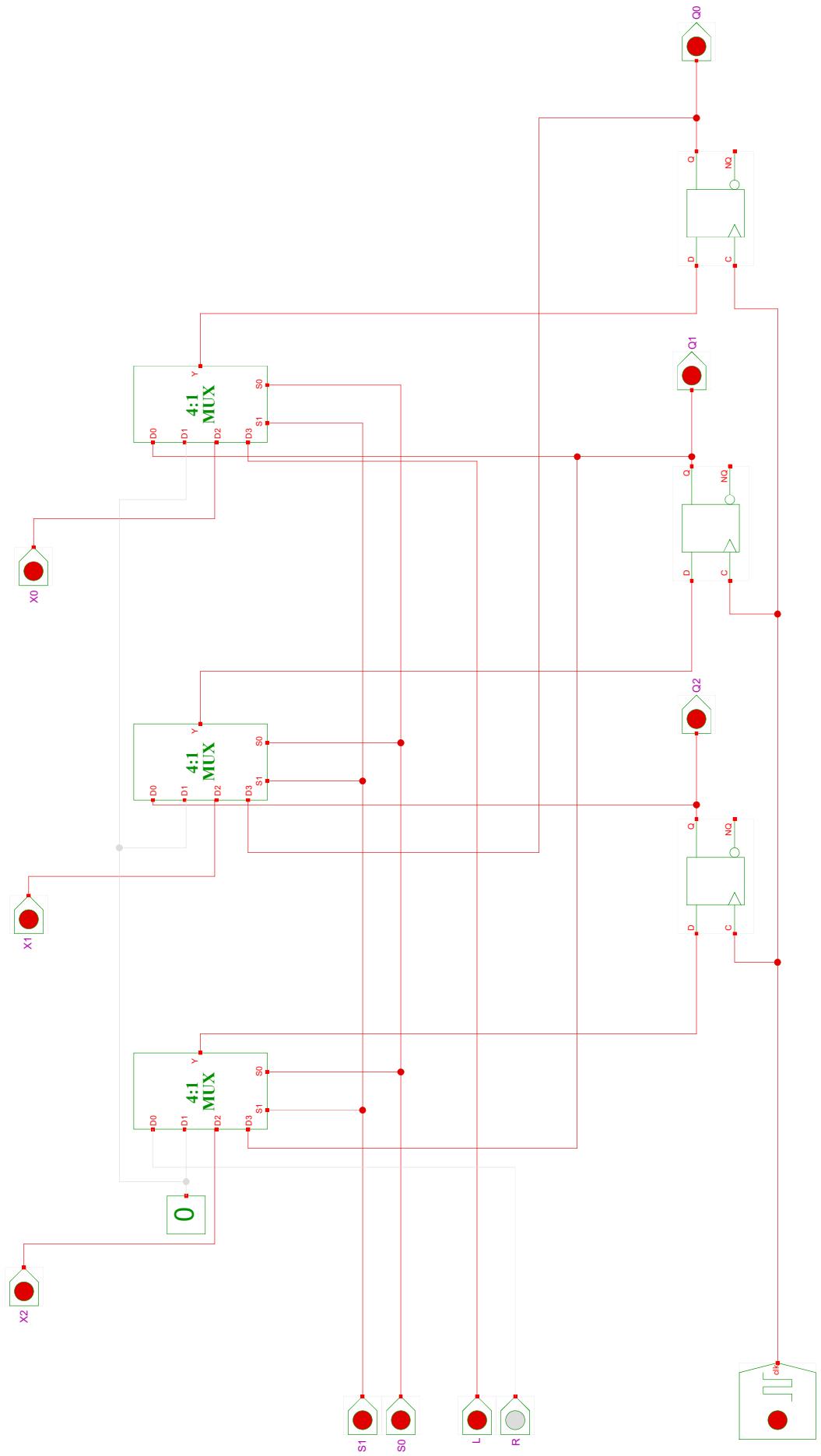

- **Die Hades Simulation:**

Der als letzte Seite angehängte Screenshot zeigt die Hades Umsetzung des oben abgebildeten steuerbaren Schieberegisters. Was auf den ersten Blick sehr kompliziert aussieht, ist es eigentlich gar nicht: Ganz oben sieht man die Eingangssignale für  $X_2, X_1, X_0$ , die initial mit 1 vorbelegt sind, zu erkennen an der roten Farbe. Sie sind, wie oben in der Abbildung, mit dem Eingang der Mux verbunden, der mit  $S_1 S_0 = 10$  weiter geschaltet wird:  $D_2$ . Am  $D_1$ -Eingang der drei Mux ist 0 fest verdrahtet, realisiert durch eine `constant0` Komponente, die mit allen  $D_1$  Eingängen über eine gemeinsame Leitung verbunden ist.

Unterhalb der Multiplexer verlaufen die Leitungen für die Steuersignale  $S_1$  und  $S_0$ , die initial ebenfalls mit 1 (rot) vorbelegt sind. Darunter liegen die Leitungen für  $L$  und  $R$ . Laut der Funktionstabelle (siehe oben) soll bei  $S_1 S_0 = 00$  rechts geschoben werden. Je nachdem, ob  $R=1$  (rot) oder  $R=0$  (grau), werden 0en oder 1en nach rechts geschoben. Ebenso beim Linksschieben, gilt  $S_1 S_0 = 11$ , dann werden bei  $L=0$  0en und bei  $L=1$  1en nach links geschoben.

Bei Aufruf der Simulation gilt  $S_1 S_0 = 11$  und  $L=1$ , sodass das Linksschieben mit 1en beobachtet werden kann.

Wie in der Funktionstabelle vorgeschrieben, wird bei  $S_1 S_0 = 10$  der Inhalt der Eingangsvariablen  $X_2, X_1, X_0$  geladen, bei  $S_1 S_0 = 01$  wird gelöscht.

Der Clockgenerator, ganz unten links im Bild, generiert eine On/Off-Endlosschleife, sodass der Nutzer den Takt nicht händisch simulieren muss.

Die Ausgänge der Multiplexer sind jeweils mit den DFFs verbunden, deren Ausgänge  $Q_2, Q_1, Q_0$  mit Ausgangssignalen verbunden sind, um die jeweiligen Zustände zu visualisieren.

- **Die Simulation besteht aus folgenden Komponenten:**

- 7 Ipins (switch)

- 3 4:1MUX

- 3 DFF

- 1 constant0

- 3 Opin (LED)

- 1 Clockgenerator

- **Besonderheit:**

In dieser Simulation wurden *Subdesigns* verwendet. Die Symbole *4:1 MUX* verstecken die Implementierung der zugrundeliegenden 4 zu 1 Multiplexer (siehe Simulation 13 dieser Reihe) und verfügen über die volle Funktionalität des enthaltenen Subdesigns. Wie bei allen verwendeten Subdesigns gilt auch hier: Klickt man mit der rechten Maustaste auf das Symbol und wählt im erscheinenden Popup-Menu den Eintrag *edit*, so öffnet sich das enthaltene Subdesign im Editor.