- **Das zugrundeliegende Schaltnetz: NF-Paralleladdierer**

Als eine Form von Paralleladdierern wird im Kurstext 1608 der Paralleladdierer in Normalformlösung wie folgt vorgestellt:

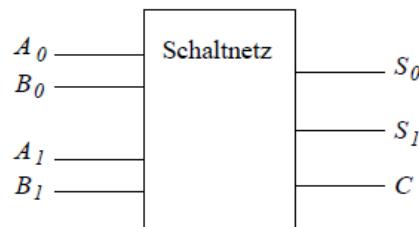

*Bei einer Normalform entsteht immer ein dreistufiges Schaltnetz mit den Ebenen NICHT, UND, ODER. Die Addierzeit bei diesem Paralleladdierer ist von der Stellenzahl der Summanden unabhängig. Sie ist konstant und beträgt 3 Laufzeiten. Der Hardwareaufwand steigt allerdings sehr schnell an. Abb. 2.22 zeigt das Blockschaltbild für die Addition von zwei 2-Bit Zahlen:*

Für die Ausgangsvariablen ergeben sich die Funktionsgleichungen in der DF:

$$\begin{aligned}

S_0 &= A_0 \overline{B}_0 \vee \overline{A}_0 B_0 \\

&= A_0 \oplus B_0 \\

S_1 &= A_0 B_0 A_1 B_1 \vee A_0 B_0 \overline{A}_1 \overline{B}_1 \vee \overline{A}_0 \overline{A}_1 B_1 \vee \\

&\quad \overline{A}_0 A_1 \overline{B}_1 \vee \overline{B}_0 \overline{A}_1 B_1 \vee \overline{B}_0 A_1 \overline{B}_1 \\

&= A_1 \oplus B_1 \oplus (A_0 B_0) \quad (\text{mit } C_1 = A_0 B_0) \\

&= A_1 \oplus B_1 \oplus C_1 \\

C &= A_1 B_1 \vee A_0 B_0 A_1 \vee A_0 B_0 B_1 \\

&= A_1 B_1 \vee (A_1 \vee B_1) A_0 B_0 \\

&= A_1 B_1 \vee (A_1 \vee B_1) C_1

\end{aligned}$$

Die Addition von  $n$ -stelligen Summanden erfordert ein Schaltnetz mit  $2n$  Eingängen und  $(n+1)$  Ausgängen. Für jeden Summenausgang müssen (ohne Minimierung)  $2^{(2n-1)}$  Min- oder Maxterme verknüpft werden. Die Anzahl der Verknüpfungsglieder für die Summenausgänge wächst mit  $n \cdot 2^{(2n-1)}$ . Ein Normalform-Paralleladdierer, der die Addition von 16- oder 32-Bit Summanden realisieren soll, ist hardwaremäßig nicht mehr realisierbar. Der Normalform-Paralleladdierer ist ein Addiernetz mit minimaler Addierzeit aber maximalem Hardwareaufwand.

- **Die Hades Simulation:**

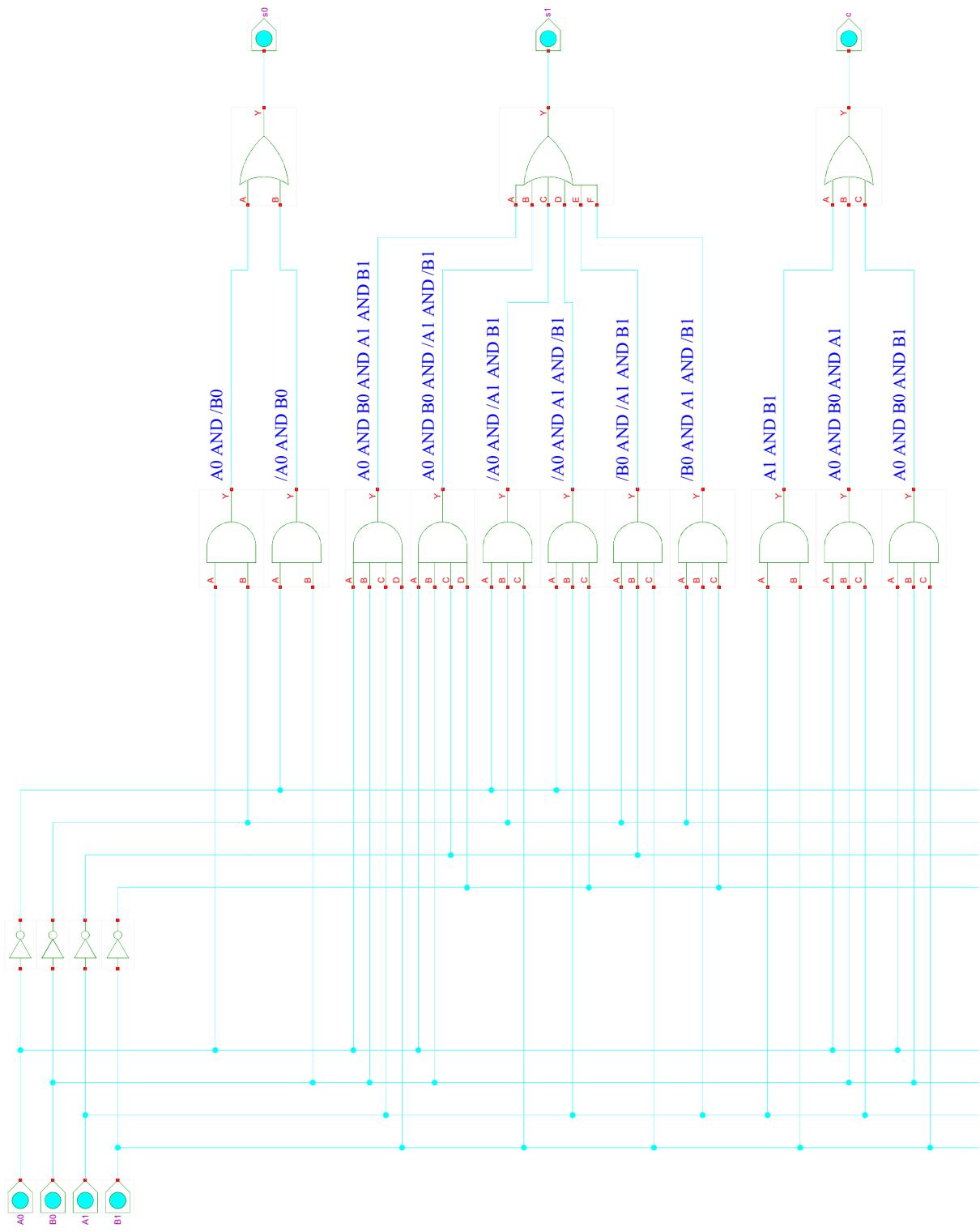

Der als letzte Seite angehängte Screenshot zeigt links die 4 Eingangssignale  $A_0, B_0, A_1, \text{ und } B_1$  für die zu addierenden Eingangsbits. Rechts befinden sich die Ausgangssignale für die Summenbits  $s_0$  und  $s_1$  sowie für das Ausgangsübertragsbit  $C$ .

Zu Beginn ist die Simulation im undefinierten Startzustand, zu erkennen an der Farbe cyan der Schalter und Verbindungen. Durch Klick auf die Schalter für die Eingangssignale belegt man die Eingangsvariablen mit 0 (grau) oder 1 (rot) und kann entsprechend das Verhalten des Normalform-Paralleladdierers im Schaltnetz verfolgen und das Additionsergebnis an den Ausgangssignalen ablesen.

Die Funktionsgleichungen wurden exakt umgesetzt. Beispiel:

Das OR-Schaltglied, dessen Ausgang  $s_0$  signalisiert, hat als Eingänge

$$\begin{aligned}\text{Eingang A: } & A_0 \wedge \bar{B}_0 \\ \text{Eingang B: } & \bar{A}_0 \wedge B_0\end{aligned}$$

realisiert also die Funktionsgleichung für  $s_0$  (siehe oben).

- **Die Simulation besteht aus folgenden Komponenten:**

- |                    |                 |                 |

|--------------------|-----------------|-----------------|

| ◦ 4 Ipins (switch) | ◦ 4 INV (small) | ◦ 3 AND2        |

| ◦ 6 AND3           | ◦ 2 AND4        | ◦ 1 OR2         |

| ◦ 1 OR3            | ◦ 1 OR6         | ◦ 3 Opins (LED) |