- **Das zugrundeliegende Schaltnetz: Ripple-Carry-Adder ohne Eingangsübertrag**

Als ein Beispiel für einen Paralleladdierer wird der Ripple-Carry-Addierer ohne Eingangsübertrag im Kurstext 1608 wie folgt vorgestellt:

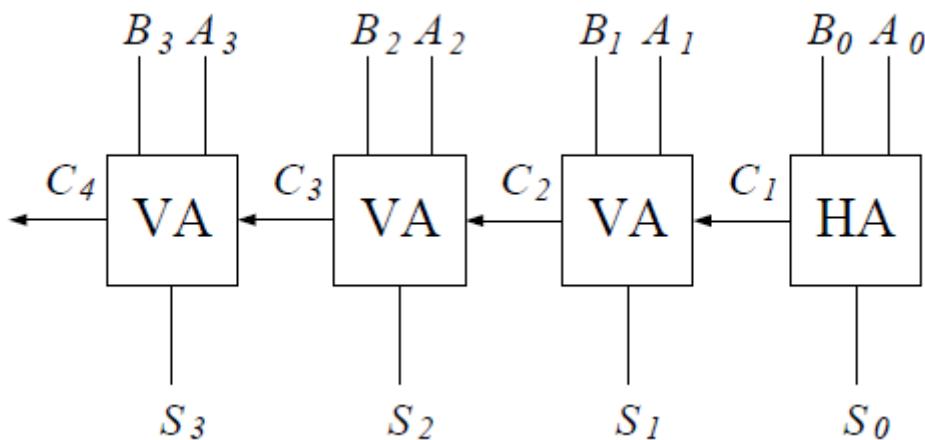

*Der Ripple-Carry Adder realisiert ein mehrstufiges Schaltnetz. Die Addition der ersten oder wertniedrigsten Stelle wird von einem HA, der ein zweistufiges Schaltnetz enthält, ausgeführt. Für jede weitere zu addierende Stelle wird ein VA nachgeschaltet, der aus den Stellenbits und dem Übertrag der voraufgehenden Stelle wiederum einen Übertrag und eine Summe bildet. Abb. 2.23 zeigt den so entstandenen Aufbau eines 4-Bit Ripple-Carry Adders:*

*Der Ripple-Carry Adder ist ein Addiernetz, bei dem Addierzeit und Hardwareaufwand linear zur Stellenzahl n wachsen.*

Quelle: Computersysteme I (2017), Kapitel 2.6.3 Paralleladdierer

- **Die Hades Simulation:**

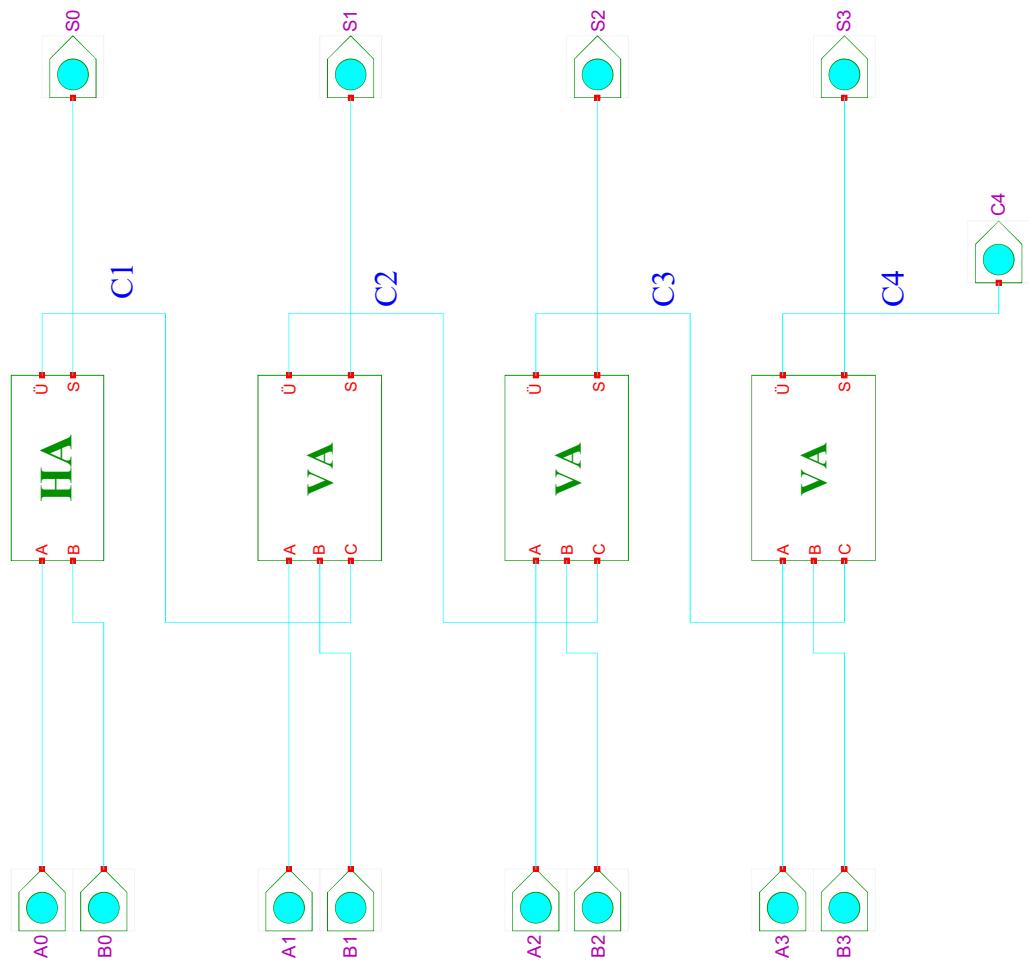

Links im als letzte Seite angehängten Screenshot sieht man die acht Eingangssignale für die zu addierenden Dualzahlen  $A_0, \dots, A_3$  und  $B_0, \dots, B_3$ , rechts die Ausgangssignale für die Summenbits  $S_0, \dots, S_3$  und das Ausgangssignal für den Ausgangsübertrag  $C_4$ .

Die Bits  $A_0$  und  $B_0$  werden in den Halbaddierer geleitet. Da dies ein Ripple-Carry-Adder ohne Eingangsübertrag ist, ist für die niedrigewertigsten Bits ein Halbaddierer ausreichend. Dessen Summenausgang ist das Ausgangssignal für  $S_0$ , sein Ausgangsübertrag ist das Eingangsübertragssignal für den ersten Volladdierer, dessen Dateneingänge die Bits  $A_1$  und  $B_1$  sind. So setzt sich das fort bis zum letzten VA, dessen Ausgangsübertrag hier in ein zusätzliches Ausgangssignal  $C_4$  geleitet wird, um einen anfallenden Übertrag besser anzeigen zu können.

Wie in anderen Simulationen dieser Reihe auch, befindet sich das Schaltnetz bei Aufruf in einem undefinierten Zustand (cyanfarbene Schalter/Verbindungen). Durch Klick auf die Schalter für die Eingangssignale weist man den Variablen die Werte 0 (grau) oder 1 (rot) zu und kann dann das Verhalten des Addierers verfolgen und die Ergebnisse an den Signalen für die Summenbits ablesen.

- **Die Simulation besteht aus folgenden Komponenten:**

- 8 Ipins (switch)

- 5 Opins (LED)

- 1 HA

- 3 VA

- **Besonderheit:**

In dieser Simulation wurden *Subdesigns* verwendet. Die Symbole HA und VA verstecken die Implementierung der zugrundeliegenden Addierer. Die Symbole sind beliebig in Toplevel-Designs einsetzbar und verfügen über die volle Funktionalität der enthaltenen Subdesigns, in diesem Falle eines Halbaddierers (sh. Simulation 05 dieser Reihe) und eines zweistufigen Volladdierers (sh. Simulation 06 dieser Reihe). Wie bei allen verwendeten Subdesigns gilt auch hier: Klickt man mit der rechten Maustaste auf das Symbol und wählt im erscheinenden Popup-Menu den Eintrag *edit*, so öffnet sich das enthaltene Subdesign im Editor.